連載|組込みシステムにおけるマルチコア

第2回 ハードウェア編

―マルチCPUとマルチコア

前回触れた「並列処理」は、単に複数の作業を同時に行うというだけではありません。実際には、CPU内部のコア構造、キャッシュ階層、メモリアクセス制御など、複雑な仕組みが密接に関係しています。

第2回では、ハードウェアとソフトウェアの両面から、並列処理を成立させるための基本アーキテクチャを紐解きます。

この連載の記事一覧

連載|組込みシステムにおけるマルチコア

1. マルチCPU

CPUの真の並列動作メカニズムは、複数のCPU(プロセッサ)が同時に異なる命令を実行して複数の異なるデータを処理するメカニズムであるMIMD(Multiple Instruction Multiple Data-stream)機構が必要となります。

まず考えられるのは、複数のCPUチップ(CPU処理装置)でシステムを構成するモデルです。

レストランを例にすると、料理担当者と電話担当者が専任で仕事をするようなイメージです。

複数のCPUを利用する古典的なシステム構成では、下記のモデルが提案されています。

1) デュアルシステム(2系統システム)

CPUを2系統または複数用意し、常に同じ処理を行って結果を相互にチェックします。一致しない場合は故障と判断します。

また、複数のCPUの実行結果を多数決によって決定する場合もあります。そうすることで、システムの信頼性を高めます。これは、故障によって人命に多大なリスクを及ぼすようなシスムに採用されます。

このアイデアは、安全実行が求められるリアルタイムプロセッサのロックステップ実行に継承されています。

2) デュプレックスシステム(2重化システム)

これは、システムの可用性を高めるマルチCPU構成モデルです。

システムを2系統用意します。通常は一方(主系CPU)で処理を行い、片方はバックアップCPUとして待機するというアイデアです。一方が障害で停止した場合、バックアップのCPUが代わりに動作することでシステムの可用性を高めるというものです。

これは組込みシステムというより、可用性が不可欠なクラウドの基幹サーバーシステムで普及しているアイデアです。

3) マルチプロセッシングシステム

2つ以上の複数のCPUで構成され、それぞれが役割分担するシステムです。

ハードウェアスレッディングと呼ばれる、真のタスクの並列実行を実現します。

以下は、マルチプロセッシングシステムの典型的なモデルです。

- CPUを直列につなぎ、データ処理をバケツリレー方式で行うタンデム実行型

- それぞれのCPUが異なる機能を分担する機能分散型

- 1つのCPUに負荷が分散しないようにする負荷分散型

- 1つのCPUで実行するソフトウェアが不具合や他のCPUに影響しないよう運用する、安全分散型

スマートフォン以前の携帯電話黎明期には、携帯電話は電話専用デバイスであり、ソフトウェアは組込みシステムとして開発されました。携帯電話のアプリケーションが多様化・複雑化していく過程で、携帯電話はフィーチャーフォン(多機能電話・俗称ガラ携)と呼ばれるようになります。フィーチャーフォンは、さまざまなアプリケーションを実行するCPUと、電話機能のみを安全に実行する通信制御CPUの2CPUで構成されました。

これは、携帯電話デバイスの安全分散・負荷分散・機能分散を考慮した必然の進化と考えます。

2. マルチコア

前述のような、複数のCPUチップでシステムを構成されるデバイスは、BOMの価格やボード実装面積の面で高価になります。

このため、組込みシステムでは、1チップの同一ダイに複数プログラムを並列実行する処理ユニット(CPUコア)を実装したマルチコアのCPUチップが採用されてきています。

1チップに実装することで、価格や実装面積において優位性があり、さらに省電力性の面でも利点があります。またプロセッサ間で情報交換する場合も、大きなサイズの共有メモリを介してプロセッサ間通信を行うことが可能になります。

マルチコアは、以下のように分類されています。

a) ホモジニアスマルチコア(同種マルチコア)

同じ命令セットの同種の実行ユニット(コア)を複数実装したマルチコアシステムであり、SMP(対照型マルチプロセス)型のマルチコアと呼ばれています。

SMP型では、単一の実行コードをすべてのコアで動作させることができます。それぞれのコアには実行ユニット、レジスタセット、L1キャッシュ、TLB、MMUを個別に持ち、それらを統括する割り込みコントローラやコアのローカルキャッシュのコア間の同期をとるスヌープ制御ユニットが実装されます。

SMP型のマルチコアは、実装するコアの個数により「Dual-Core(2コア)」「Quad-Core(4コア)」「Octa-Core(8コア)」と呼びます。ちなみに、10コア以上の場合は「メニーコア(Many-core)」と呼び、SMP型マルチコアとは異なった技術アプローチが行われます。

現在、組込みシステムで利用されるのは、Quad-Coreまでのようです。

b) ヘテロジニアスマルチコア(異種マルチコア)

異なる命令セットのプロセッサが同一CPUの同一ダイに実装されたマルチコアCPUを、ヘテロジニアスマルチコアと呼んでいます。

例えば、汎用処理が得意なマイクロコントローラと、デジタル信号処理に特化したDSPを同一ダイに実装したCPUがこのタイプです。

高い処理能力を持つアプリケーションプロセッサ(例えばArm® Cortex®-A)と、リアルタイム処理に特化するプロセッサ(Arm® Cortex®-R)やマイクロコントローラ(Arm® Cortex®-M)を組み合わせたタイプも存在します。

Arm®のbig.LITTLE構成は、命令セットが同じですが、クラスタと呼ぶパフォーマンスや電力消費が異なるSMPマルチコアセットを2系統実装しており、使用場面に合わせて実行するクラスタを切り替えて使用するアーキテクチャです。

※ 実際には、big.LITTLEは説明したクラスタスイッチの他にさまざまなアイデアがあります。

big.LITTLEは、高機能OSが動作するスマートフォンやタブレットのようなモバイルデバイスに採用されています。これをヘテロジニアスマルチコアと呼ぶ場合もありますが、ちょっと違和感を覚えます。

現在のアプリケーションプロセッサと呼ばれる高機能なSoCには、アプリケーションプロセッサ(AP)の他に、リアルタイムプロセッサ(RP)、GPU(グラフィックプロセッサ)、DSP(デジタルシグナルプロセッサ)、ISP(カメラ画像プロセッサ)、NSP(ニューラルネットワークシグナル・プロセッシングユニット)で構成される複雑な物もあります。

こうなると、このCPUはヘテロジニアスなのか、ホモジニアスなのかと分類するのも空しくなりますね。

3. 並列化の粒度

並列化の粒度として、以下の分類があります。

- 大きなアプリケーション機能

- 従来ソフトウェアのタスク・プロセス単位

- 通常プログラム(逐次処理記述)内の並列実行可能な部分

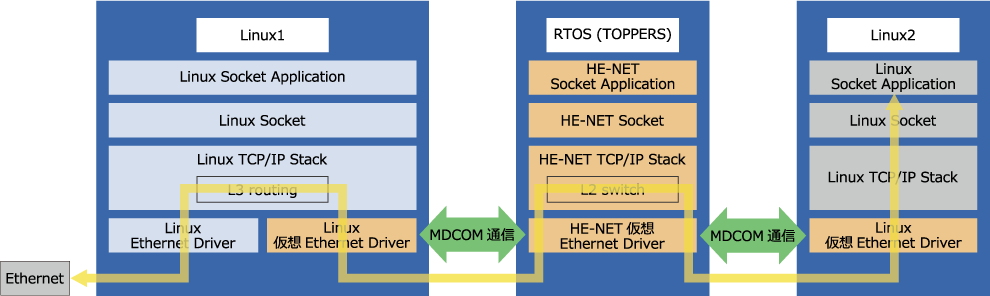

(1) は、分散処理技術の分野として発展しています。組込みシステムではプリンタ複合機がこのタイプです。

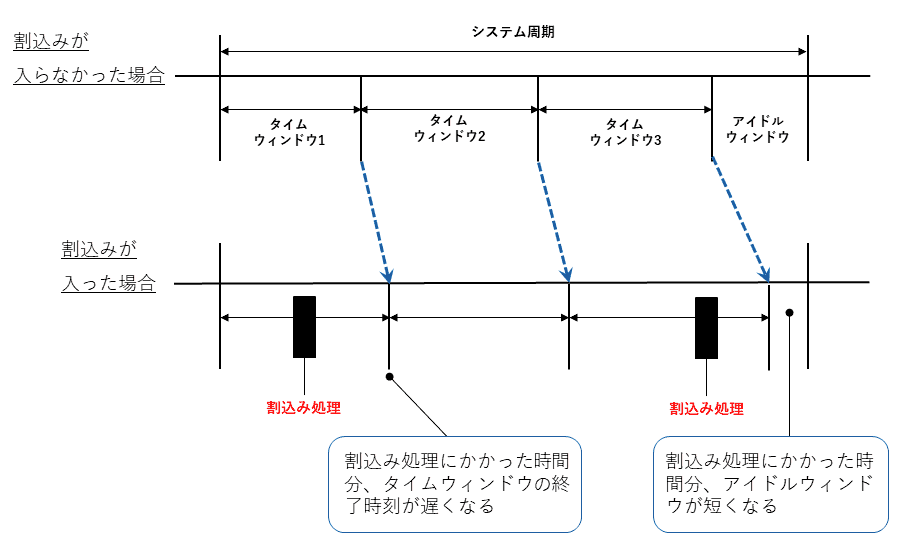

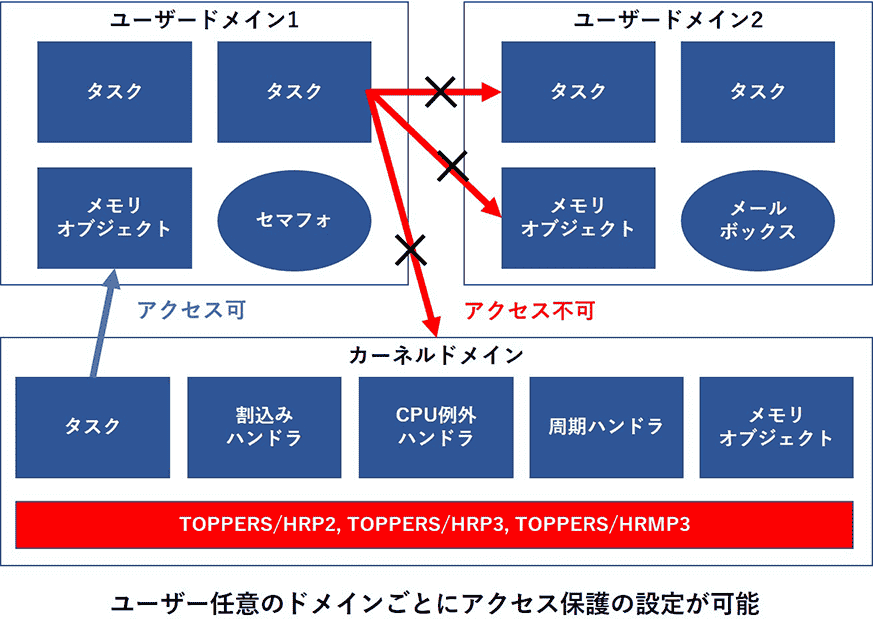

(2) は、OS・RTOSのタスク(スレッド)・プロセスのスケジューリング技術の拡張として発展しています。

実行単位であるタスクは、コアごとに実行スケジューリングされます。特定のタスク・プロセスを特定のCPUコアで実行するよう割り当てすることを「プロセッサアフィニティ」と呼びます。

RTOSの場合、静的にプロセッサアフィニティを決定して、機能分散・負荷分散するのが一般的です。RTOSは、実行タスクの動的なコア移動を行わないのが一般的です。

一方、Linuxに代表される汎用OSをベースとした組込みシステムOSでは、各コアの負荷状態を監視して、極端に負荷が偏った場合には、プロセスが実行するコアを移動することで負荷の平滑化を行います。これを「ロードバランシング」と呼びます。

(3) は、言語レベルの並列化の話であり、並列化コンパイラ技術に関連します。ノイマン型コンピュータの特性に従い、逐次記述されたプログラムから並列に実行することが可能な部分を抽出し、異なるハードウェアスレッドで並列動作する実行コードを生成します。

完全な並列化コンパイラ

完全な並列化コンパイラは、逐次記述されたソースコードを解析し、並列化が可能な箇所を自動で抽出します。これを、他コアで動作するタスクまたはスレッドと呼ばれる実行単位に変換して、並列実行のコードを自動生成します。このメリットは、プログラマが並列化の知識や意図がなくても、マルチコア実行コードを作成できることです。

完全な並列化コンパイラでは、主にループ処理中のデータの並列性に注目して並列化されます。この並列化コードの生成は、コンパイラの最適化の拡張としてコンパイラ内部に実装できます。

手動の並列化コンパイラ

逐次記述されたソースコードにプログラマが並列化の指示文(例えばC言語では#pragma文など)を挿入記述することで、「並列化の範囲」「Fork(並列実行分岐)& Join(分岐後の待ち合わせ)の同期」や「メモリリソースの排他処理」などを、明示的に並列化コンパイラに指示します。並列化はプリプロセッサによって解釈・ソースコード生成を行うので、プログラミング言語翻訳機(コンパイラ)は通常のコンパイラを使用することができます。

手動の並列化コンパイラの例として、OpenMPがこれに該当します。多くのコンパイラがOpenMPをサポートしています。

手動の並列化のメリットは、プログラマの並列実行に関する知識を活かし、プログラマが意図した並列処理を実現できる点です。

いずれの場合も並列化コンパイラだけでは並列化は実現できず、マルチコアをサポートしたOSのタスク(スレッド)管理のサポートやそのAPIがあっての技術と言えます。

この連載の記事一覧

連載|組込みシステムにおけるマルチコア

今回は、並列化の基本とマルチCPU・マルチコアの考え方を理解しました。

第3回は、実際の開発現場における並列化支援技術、マルチコアRTOSやデバッガ技術、さらにTOPPERSカーネルのマルチコア拡張など、より実践的な内容に踏み込んでいきます。